世界日趋自动化。我们的日常生活,从更智能家庭(AC、照明和大型家用电器)到更轻松、惬意的汽车旅行,都体现出了不断提高自动化程度的强大主动力。这需要大量的处理器和逻辑器件!但逻辑器件是如何控制所有这些电机、LED 和继电器的呢?外设、电机和低侧驱动器是实现该目标不可或缺的组成部分。您可能已经知道大部分应用中所使用的极其标准的驱动器 — 达林顿晶体管。但随着我们努力构建更优异的创新解决方案,我觉得有必要问一个问题:我们应如何让这一标准变得更好?

标准驱动器是什么样的?

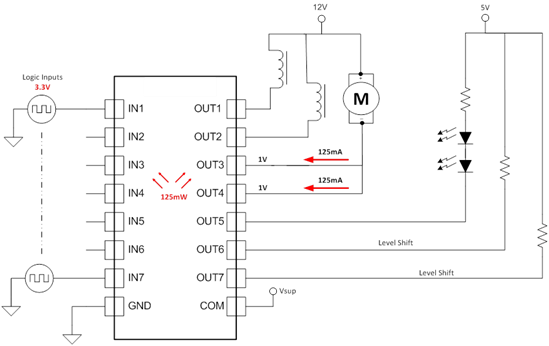

如今,最简单也是最常见的外设驱动器是达林顿晶体管阵列。这种低侧驱动器有助于逻辑器件驱动或控制具有更高电源要求的器件(如图 1 所示):

图 1:达林顿低侧驱动器

在当前系统中,设计人员使用包含多个达林顿对的阵列控制完整的系统。这类系统通常可以用支持 TTL 或 5V CMOS 的逻辑器件驱动每通道高达 50V 及 500mA 的器件。当电流要求过高、使用单通道无法驱动时,可将通道并联,帮助平均分配电流负载(如图 2 所示)。

图 2:达林顿阵列驱动器

但是,采用这种架构也有其自身的折中权衡和限制。最大问题之一是,当外设驱动器的大部分(甚至全部)通道都过载时,需要增大电路板尺寸。这随后需要使用一个附加驱动器来划分其中的电流需求。另一个缺点是该器件会增加系统功耗。由于堆栈 NPN 晶体管的原因,该器件输出低侧的电压会增加约 0.7V。现在,该系统的功耗将为:

PD = VOL*IO

PD = (~0.7V + 2Ω*IO) * Io

如何让标准更好?

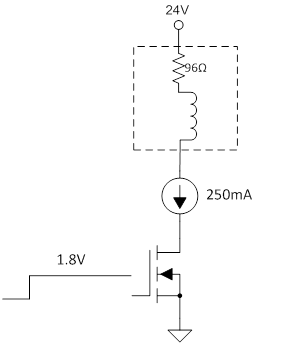

这些折中权衡的一个解决方案是使用 NMOS 晶体管,而非达林顿对。该低侧驱动器架构具有更低的功耗,支持从 1.8V 到 5V 的所有 GPIO 电平输入。

图 3:NMOS 低侧驱动器

该配置允许我们采用一种(和使用达林顿对相同)的方法驱动外设,可显著降低功耗:

PD = VOL*IO

PD = (2Ω*IO) * Io

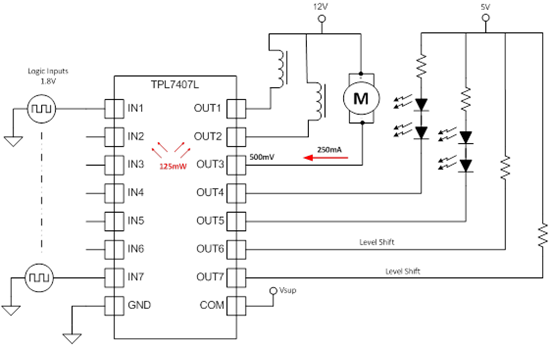

德州仪器 (TI) 最新外设驱动器 TPL7407L 是一款复制这种架构的 7 通道 NMOS 低侧驱动器阵列。该器件不仅可帮助我们替代任何标准 7 通道达林顿驱动器,同时还可将功耗保持在标准解决方案以下。此外,该器件还具有更大的电流支持,可实现将更大的电流分配给单通道或比标准器件更少的通道。

图 4:7 通道 NMOS 低侧驱动器

外设驱动技术广泛用于大型家用电器、HVAC、汽车以及楼宇自动化等高电压应用。如果您已经拥有或者正在设计将达林顿晶体管阵列用作外设驱动器的系统,那么使用该器件,无需进行大量重复设计便可改进系统。这个简单的改变能将您的设计带到全新的高度,使系统性能更加优异!

原文请参见: http://e2e.ti.com/blogs_/b/analogwire/archive/2014/06/20/upgrading-the-standard-a-better-way-to-drive-peripherals.aspx

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。